# F15353 2-wire Real-time Clock

Release Date: Sep, 2008 Version: 0.12P

# F15353 Datasheet Revision History

| Version         | Date      | Page | Revision History                                              |

|-----------------|-----------|------|---------------------------------------------------------------|

| 0.10P Jan, 2008 |           |      | Preliminary version                                           |

|                 |           |      | Modify some contents in General Description                   |

| 0.11P           | Jul, 2008 | 4    | Current consumption spec changed to 0.55uA at 3.0V            |

|                 |           |      | Add TSSOP-8 package for option                                |

|                 |           | 4    | supply voltage as low as <del>1.2</del> 1.1 V (min.)          |

|                 |           | 5    | Add TSSOP-8 pin configuration                                 |

|                 |           | 9    | Operating voltage <del>3.0</del> 1.3V                         |

|                 |           |      | Input low voltage <del>0.6</del> 0.4V                         |

| 0.12P           | Sep, 2008 | 12   | Revise 6.4 description                                        |

|                 | ()        | 19   | Add "Caution: The figure range which can be corrected is that |

|                 |           |      | the calculated value is from 0 to 62."                        |

|                 |           | 33   | Remove redundant register 7.9-7.13                            |

|                 |           | 37   | Figure 18: F15353 <del>S</del> Application Circuit            |

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Fintek for any damages resulting from such improper use or sales.

۰.

## Table of Contents

| 1 | GE          | NERAL DESCRIPTION                                  | 4  |

|---|-------------|----------------------------------------------------|----|

| 2 | <b>FE</b> A | ATURE                                              | 4  |

| 3 | DIN         | CONFIGURATION                                      | 5  |

| - |             |                                                    |    |

| 4 | PIN         | DESCRIPTION                                        |    |

|   | 4.1.        | Power Pin                                          |    |

| 4 | 4.2.        | CRYSTAL OSCILLATOR PIN                             |    |

| 4 | 4.3.        | INTERRUPT PIN                                      |    |

|   | 4.4.        | I2C INTERFACE PIN                                  |    |

| 5 | EL          | ECTRICAL CHARACTERISTIC                            | 8  |

| 6 | ы           | NCTIONAL DESCRIPTION                               | 0  |

| U | FUI         | Power Supply Voltage Detector                      |    |

|   | 6.1         | POWER SUPPLY VOLTAGE DETECTOR                      | 9  |

|   | 6.2         | POWER SUPPLY VOLTAGE DETECTOR                      |    |

|   | 6.3         | REAL-TIME DATA                                     |    |

|   | 6.4         | INVALID DATE AND END-OF-MONTH PROCESS              |    |

|   | 6.5         | INTERRUPT FUNCTION                                 |    |

|   | 6.6         | ALARM INTERRUPT FUNCTION                           | 18 |

|   | 6.7         | CLOCK ADJUSTMENT FUNCTION                          |    |

|   | 6.8         | I2C INTERFACE FUNCTION                             |    |

|   | 6.9         | DATA WRITING                                       |    |

|   | 6.10        | COMMUNICATION DATA CONFIGURATION                   |    |

| 7 | RE          | GISTER DESCRIPTION (I2C ADDRESS = 0X6X)            | 26 |

| , | 71          | STATUS REGISTER_1 ACCESS (COMMAND 000B)            | 26 |

|   |             |                                                    | 26 |

|   | 7.2         | STATUS REGISTER_2 ACCESS (COMMAND 001B)            |    |

|   | 7.3         | REAL-TIME DATA 1 ACCESS, YEAR DATA (COMMAND 010B). |    |

|   | 7.4         | REAL-TIME DATA 2 ACCESS, HOUR DATA (COMMAND 011B)  |    |

|   | 7.5         | INT1 REGISTER_1 ACCESS (COMMAND 100B)              |    |

|   | 7.6         | INT1 REGISTER_2 ACCESS (COMMAND 101B)              |    |

|   | 7.7         | CLOCK ADJUSTMENT REGISTER ACCESS (COMMAND 110B)    |    |

| , | 7.8         | FREE REGISTER ACCESS (COMMAND 111B)                | 33 |

| 8  | ORDERING INFORMATION                | 34 |

|----|-------------------------------------|----|

| 9  | PACKAGE DIMENSIONS (8-SOP, 8-TSSOP) | 35 |

| 10 | APPLICATION CIRCUIT                 | 37 |

# **1** General Description

The F15353 which is a low current consumption 2- wire CMOS real-time clock operates under 1.3V to 3.6V. The current consumption is only 0.55uA and operation voltage is 1.1V as time keeping. In a system that operates on a backup battery, the free register incorporated in the real-time clock can be used for the user backup memory function. The user register can hold data on a supply voltage as low as 1.1 V (min.), so the data stored in the register before the main power supply was removed and can be recalled any time after the power is reconnected.

A clock adjustment function that enables wide range correction of deviation in the frequency of the crystal oscillator at a minimum resolution of 1 PPM is integrated in the F15353. The clock adjustment value can be set in accordance with changes in the temperature. It is possible to make the realization of clock function that retains a high degree of accuracy regardless of temperature variation by combining with a temperature sensor.

# 2 Feature

- ♦ Low Current Consumption: 0.55uA, Typical (VDD = 3.0V, Ta = 25°C)

- Operate Voltage Range: 1.3 to 3.6V

- Minimum Time Keeping Operation Voltage: 1.1V

- Built-in Clock Adjustment Function

- Built-in Free User Register

- Built-in Alarm Interrupt

- Built-in Flag Generator at Power down or Power on

- Built-in Constant Voltage Circuit

- Built-in 32KHz Crystal Oscillator Circuit (Cd Built-in, Cq External)

- Auto Calendar up to the Year 2099, Automatic Leap Year Calculation Function

- ♦ I2C Interface

- Powered by 3.3VCC and packaged in SOP-8 and TSSOP-8

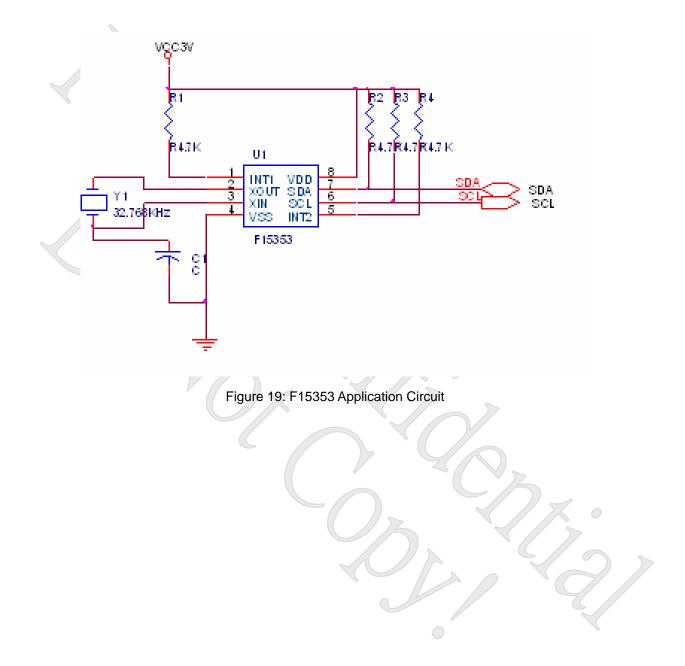

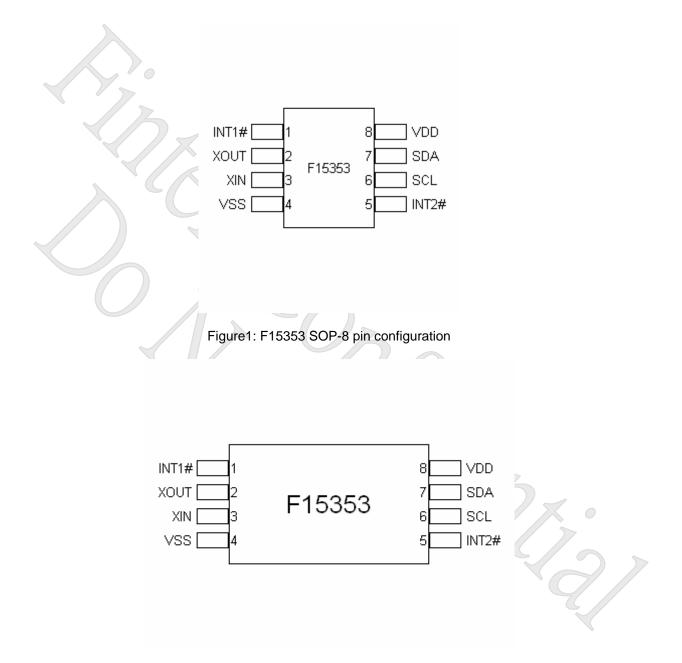

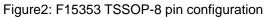

# 3 Pin Configuration

# 4 Pin Description

| Р                    | - Power pins                                                                                         |

|----------------------|------------------------------------------------------------------------------------------------------|

| IN <sub>st</sub>     | - TTL level input pin with schmitt trigger                                                           |

| I/OD <sub>1ost</sub> | - TTL level bi-directional pin with schmitt trigger, Open-drain output with 10 mA sink capability at |

|                      | VDD=3.0V                                                                                             |

| OD <sub>5</sub>      | - Output pin with 5mA sink capability at VDD=3.0V                                                    |

| AIN                  | - Input pin (Analog).                                                                                |

| AOUT                 | - Output pin (Analog).                                                                               |

#### 4.1. Power Pin

| Pin No. | Pin Name | Туре | Description      |

|---------|----------|------|------------------|

| 4       | VSS      | Р    | Ground           |

| 8       | VDD      | Р    | Power supply pin |

#### 4.2. Crystal Oscillator Pin

| Pin No. | Pin Name | Туре | PWR | Description                               |

|---------|----------|------|-----|-------------------------------------------|

| 2       | XOUT     | AOUT | VDD | Crystal oscillator connect pin, 32.768KHz |

| 3       | XIN      | AIN  | VDD | Crystal oscillator connect pin, 32.768KHz |

#### 4.3. Interrupt Pin

| Pin No. | Pin Name | Туре | PWR | Description                                                                                                                                                                                                        |  |  |  |

|---------|----------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | INT1#    | OD₅  | VDD | Interrupt 1 signal output pin. Depending on the mode set by<br>INT1 register_1 and the status register, it outputs low or a clock<br>when the time is reached. It is disabled by rewriting<br>the status register. |  |  |  |

| 5       | INT2#    | OD₅  | VDD | Interrupt 2 signal output pin. Depending on the mode set by<br>INT1 register_2 and the status register, it outputs low c<br>clock when time is reached. It is disabled by rewriting the status<br>register.        |  |  |  |

۰.

#### 4.4. I2C Interface Pin

| Pin No. | Pin Name                     | Туре             | PWR | Description                                                                                                                                                                                     |  |  |  |  |  |

|---------|------------------------------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 6       | SCL                          | IN <sub>st</sub> | VDD | Serial clock input pin. Since signal processing is done on<br>the SCL signal rising/falling edge, give great care to the<br>rising/falling time and comply strictly with the<br>specifications. |  |  |  |  |  |

| 7       | SDA I/OD <sub>1ost</sub> VDD |                  | VDD | Serial data I/O pin. Normally, it is pulled up to the $V_{DD}$ voltage by a resistor and connected with another open-drain output or open-collector output device via a wired-OR connection.    |  |  |  |  |  |

# **5** Electrical Characteristic

### 5.1 Absolute Maximum Ratings

| PARAMETER             | RATING          | UNIT |

|-----------------------|-----------------|------|

| Power Supply Voltage  | -0.3 to 3.6     | V    |

| Input Voltage         | -0.3 to VDD+0.3 | V    |

| Operating Temperature | 0 to +70        | °C   |

| Storage Temperature   | -55 to 150      | ° C  |

Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and

reliability of the device

#### 5.2 DC Characteristics

#### $(Ta = 0^{\circ} C \text{ to } 70^{\circ} C, VDD = 3.0V \pm 10\%, VSS = 0V)$

| PARAMETER                                 | SYM.         | MIN.      | TYP.      | MAX.      | UNIT    | CONDITIONS                           |

|-------------------------------------------|--------------|-----------|-----------|-----------|---------|--------------------------------------|

| Operating Voltage                         | VDD          | 1.3       | 3.3       | 3.6       | V       |                                      |

| Current Consumption 1                     | IDD1         |           | 0.55      | 0.93      | uA      | Out of communication                 |

| Current Consumption 2                     | IDD2         |           | 6         | 14        | uA      | During communication<br>(SCL=100KHz) |

| I/OD <sub>10st</sub> - TTL level and schr | nitt trigger | bi-direct | tional pi | ר with 10 | ) mA so | urce-sink capability                 |

| Input Low Voltage                         | VIL          |           |           | 0.4       | V       |                                      |

| Input High Voltage                        | VIH          | 2.4       |           |           | V       |                                      |

| Hysteresis                                | )            |           | 0.3       |           | V       |                                      |

| Output Low Current                        | IOL          | 5.0       | 10        |           | mA      | VOL = 0.4V                           |

| Input High Leakage                        | ILIH         | -0.5      |           | +0.5      | μA      |                                      |

| Input Low Leakage                         | ILIL         | -0.5      |           | +0.5      | μΑ      |                                      |

| $OD_5$ – Output pin with 5mA              | sink capabi  | ility     |           | 5         |         |                                      |

| Input Low Voltage                         | VIL          |           |           | 0.4       | V       |                                      |

| Input High Voltage                        | VIH          | 2.4       |           |           | V       |                                      |

| Hysteresis                                |              |           | 0.3       |           | V       |                                      |

| Output Low Current                        | IOH          | 3.0       | 5.0       |           | mA      | VOL = 0.4 V                          |

| Input High Leakage                        | ILIH         | -0.5      |           | +0.5      | μA      |                                      |

| Input Low Leakage                         | ILIL         | -0.5      |           | +0.5      | μA      |                                      |

| IN <sub>ts</sub> – TTL level input pin an | d schmitt tr | igger     |           |           |         | _                                    |

| Input Low Voltage                         | VIL          |           |           | 0.4       | V       |                                      |

| Input High Voltage                        | VIH          | 2.4       |           |           | V       |                                      |

| Hysteresis                                |              |           | 0.3       |           | V       |                                      |

| Input High Leakage                        | ILIH         |           |           | +0.5      | μΑ      |                                      |

| Input Low Leakage                         | ILIL         | -0.5      |           |           | μΑ      |                                      |

# 6 Functional Description

#### 6.1 Power Supply Voltage Detector

Bit 7, POC flag, of status register\_1 is set to 1 ("80h") by the power-on detector and an 1Hz clock is output from the INT1# pin. The oscillation frequency is adjustable. In the common condition, the F15353 must be initialized at power-on. Initialization is performed by setting "1" to bit 0, RESET flag, of the status register\_1. After the initialization, the POC flag is set to "0". In the common operation of the power-on detector, the supply voltage is held at 0Vand then increasing it.

The state of every register after initialization is as following:

| Real-time data register   | 00(year),01(month), 01(day), 0(day of week), 00(hour),   |  |  |  |  |  |  |

|---------------------------|----------------------------------------------------------|--|--|--|--|--|--|

|                           | 00(minute), 00(second)                                   |  |  |  |  |  |  |

| Status register_1         | "0 0 0 0 b3 b2 b1 0"b (The b3, b2, and b1 data of status |  |  |  |  |  |  |

|                           | register_1 after initialization are set in b3, b2, b1)   |  |  |  |  |  |  |

| Status register_2         | "00"h                                                    |  |  |  |  |  |  |

| INT1# register_1          | "00"h                                                    |  |  |  |  |  |  |

| INT1# register_2          | "00"h                                                    |  |  |  |  |  |  |

| Clock adjustment register | "00"h                                                    |  |  |  |  |  |  |

| Free register             | "00"h                                                    |  |  |  |  |  |  |

Table 1: Initialization States of Register

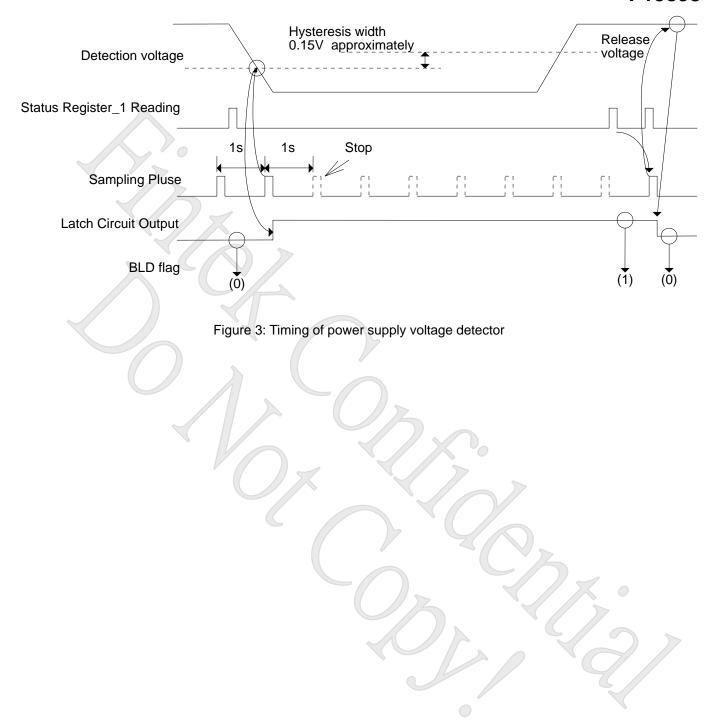

#### 6.2 Power Supply Voltage Detector

There is an internal power supply voltage detector, which monitors the power supply voltage drops by reading the BLD flag, in the F15353. If the power supply voltage drops under the detect voltage (typical 1.2v), the BLD latch circuit latches "H" level. Bit 6, BLD flag, of the internal status register\_1 is set to "1", and the sampling is stopped. If the BLD flag is detected "1", the detection is stopped until the initialization is performed or the flag is read by the status register\_1 access command, and "1" is held in the BLD flag. The resume condition of sampling operation is the subsequent communication action initialized or the BLD flag read only. If the BLD flag is "1" after the power supply voltage is recovered, it must be initialized additionally.

۰.

#### 6.3 Real-time Data

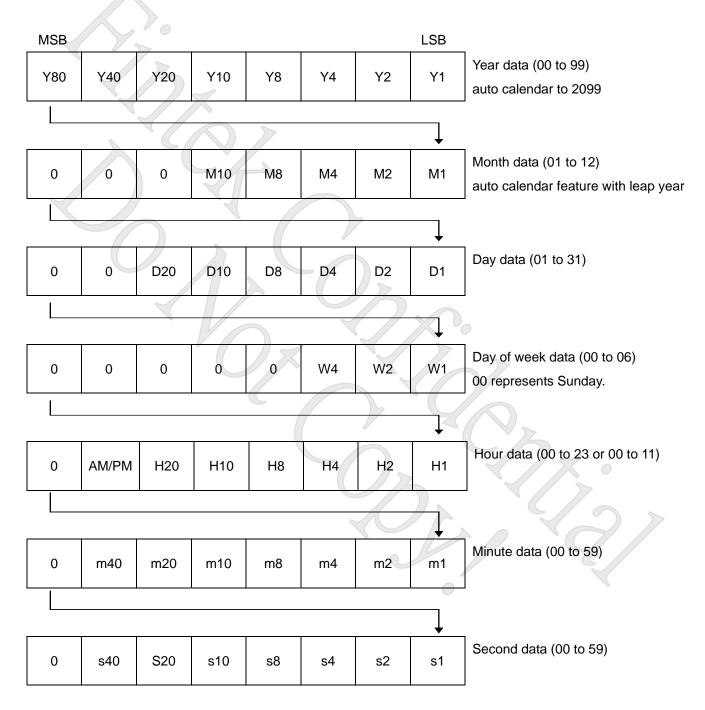

The real-time data is stored in a 56-bit register in BCD code of year, month, day, day of week, hour, minute, and second data. The data from the LSB which is the first digit of the year is transmitted or received by read/write command performed by the real-time access.

#### 6.4 Invalid Date Process

When the real time data is written, the invalid data will be corrected immediately as Table 2.

| Register         | Normal Data | Error Data                 | Result |

|------------------|-------------|----------------------------|--------|

| Year data        | 00 to 99    | XA to XF, AX to FX         | 00     |

| Month data       | 01 to 12    | 00, 13 to 19, XA to XF     | 01     |

| Day data         | 01 to 31    | 00, 32 to 39, XA to XF     | 01     |

| Day of week data | 0 to 6      | 7                          | 0      |

| Hour data*1      | 1           |                            |        |

| (24-hour)        | 0 to 23     | 24 to 29, 3X, XA to XF     | 00     |

| (12-hour)        | 0 to 11     | 12 to 19, 2X, 3X, XA to XF | 00     |

| Minute data      | 00 to 59    | 60 to 79, XA to XF         | 00     |

| Second data      | 00 to 59    | 60 to 79, XA to XF         | 00     |

Table 2: Process of Invalid Date

\*1 For 12-hour expression, setting AM/PM flag, and the flag is ignored in 24-hour expression. "0" for 0 to 11 o'clock and "1" for 12 to 23 o'clock are read in a read operation.

#### 6.5 Interrupt Function

The INT1# pin output mode is selected by the INT1AE, INT1ME, and INT1FE flags of the status register02. The INT2# pin output mode is selected by the INT2AE, INT2ME, and INT2FE flags of the status register02, similarly.

#### 6.5.1 Alarm Interrupt Output

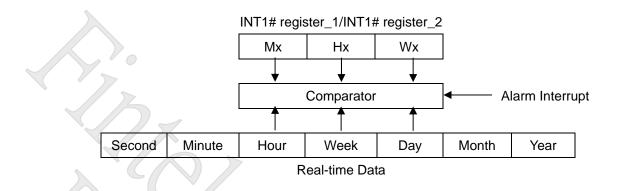

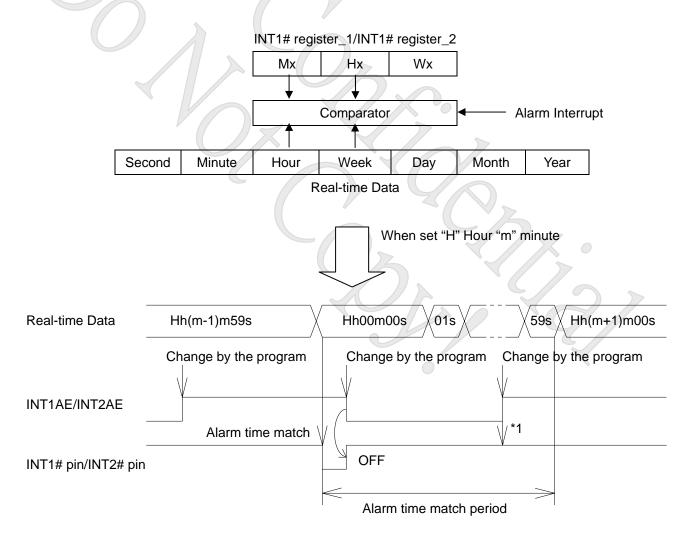

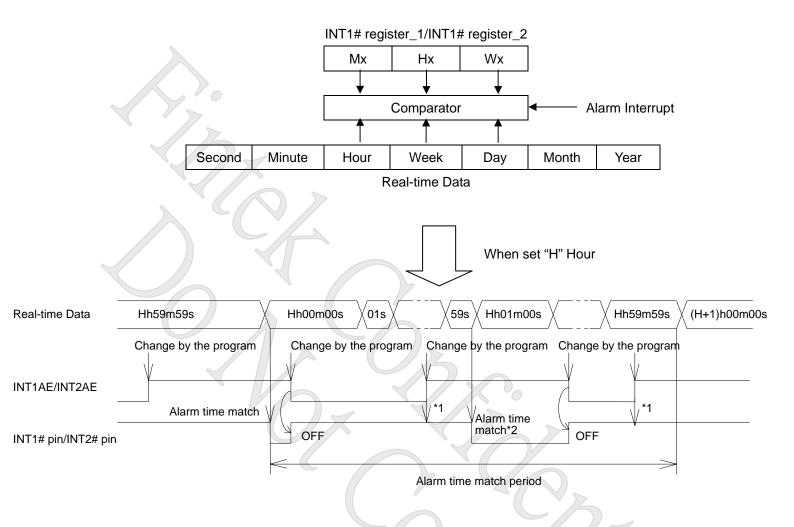

If the INT1# or INT2# pin output mode is set to the alarm setting, the INT1# or INT2# pin will pull low as the set data reached. The set data, the day of week, the hour, and the minute, are stored in INT1 register\_1 (command 100b) or INT1 register\_2 (command 101b). To Rewrite INT1AE or INT2AE of status register\_2 to "0" will release the output from low to high.

Ex:

32kE=0, INT1ME=INT1FE=0 (INT1# pin output mode), INT2ME=INT2FE=0 (INT2# pin output mode) Alarm enable flag: In case of AxWE=AxHE=AxmE="1"

32kE=0, INT1ME=INT1FE=0 (INT1# pin output mode), INT2ME=INT2FE=0 (INT2# pin output mode) Alarm enable flag: In case of AxWE="0" AxHE=AxmE="1"

32kE=0, INT1ME=INT1FE=0 (INT1# pin output mode), INT2ME=INT2FE=0 (INT2# pin output mode) Alarm enable flag: In case of AxWE=AxmE="0", AxHE="1"

\*1 Once it clears, even if it enables again within a coincidence period, "L" will not be output from an INT1# or INT2# pin.

\*2 "L" is output again from INT# pin at the time of change of the following part when an alarm output is turned on by change by the program within a coincidence period.

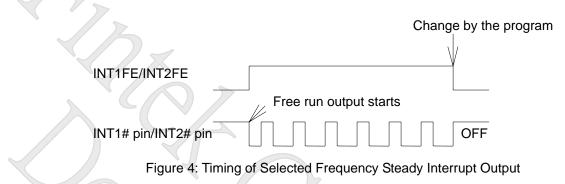

#### 6.5.2 Selected Frequency Steady Interrupt Output

Set the status register\_2 and the INT1# or INT2# pin output mode is set to the selected frequency steady interrupt output. The set clock output follows the frequency data set in INT1# register\_1 or register\_2.

#### Ex:

```

32kE=0, INT1ME=0, INT1AE=Don't care (0 or 1) INT2ME=0 INT2AE=Don't care (0 or 1)

```

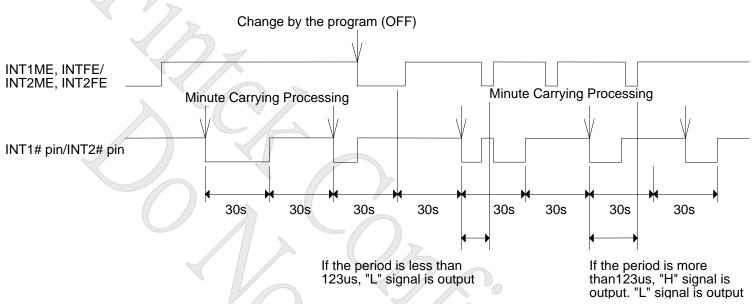

#### 6.5.3 Per-minute edge interrupt output

If INT1# or INT2# pin output mode is set as the per-minute edge interrupt, INT1# or INT2# will pull low as the first minute carry is performed. Since the output is held, to rewrite 32kE, INT1AE, INT1ME, and INT1FE of the register\_2 to "0" sets the output to high (OFF state) in INT1# pin output mode. IN INT2# mode, to rewrite INT2AE, INT2ME, and INT2FE of the register\_2 to "0" or INT2AE of status register\_2 to "0" will release the output from low to high.

Ex:

32kE=0, INT1ME=0, INT1AE=Don't care (0 or 1) INT2ME=0 INT2AE=Don't care (0 or 1)

|                     | Change by the program                                  |

|---------------------|--------------------------------------------------------|

| INT1ME/INT2ME       |                                                        |

|                     | Minute Carrying Processing                             |

|                     |                                                        |

| INT1# pin/INT2# pin | OFF                                                    |

|                     | ← →                                                    |

|                     | If the period is less than 123us, "L" signal is output |

|                     | 123us, "L" signal is output                            |

Figure 5: Timing of Per-minute Edge Interrupt Output

#### 6.5.4 Per-minute steady interrupt output1

If INT1# or INT2# pin output mode is set as the per-minute steady interrupt, INT1# or INT2# will pull low as the first minute carry is performed. The data is set in register\_2. A whole cycle of clock is 1 minute (50% duty) is output from INT1# or INT2# pin.

Ex:

32kE=0, INT1AE=0 (INT1# pin output mode) INT2AE=0 (INT2# pin output mode)

Figure 6: Timing of Pre-minute Steady Interrupt Output1

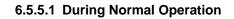

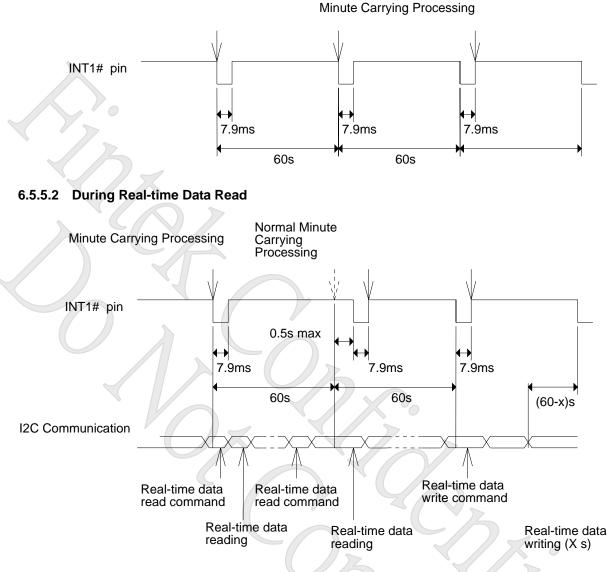

#### 6.5.5 Per-minute steady interrupt output2 (INT1# pin output mode only)

If INT1# or INT2# pin output mode is set as the per-minute steady interrupt, INT1# will pull low as the first minute carry is performed. The output is the period of 7.9ms in synchronization with the minute carry processing inside the IC. However, when real-time data is read, the minute carry processing is delayed by a maximum of 0.5 s and accordingly low output from the INT1# pin is also delayed by 0.5s maximum. When the second data is rewritten by a real-time data write command, counting starts from the rewritten second data and as a result, the output interval during that period may become either longer or shorter.

Figure 7: Time of Pre-minute Steady Interrupt Output2

Caution:

1. If Per-minute edge interrupt output mode or Per-minute steady interrupt mode is chosen, there is no difference between INT1 register\_1 register\_2.

2. When the output mode is changed, take care to the state of INT1 regisert\_1 or register\_2 and the output

#### 6.5.6 During Power-on Detector Operation

When power is applied to this IC, power-on detection circuit operates, status register\_1 is set to "80h" (bit 7 (POC flag) of status register\_1 is set to 1) via the power-on detection circuit, and a 1 Hz clock is output from the INT1# pin.

# Ex: INT2AE=INT2ME=INT2FE=32kE=INT1AE=INT1ME=0 Change by reset command INT1FE INT1# pin OFF 0.5s 0.5s Figure 8: INT1# pin output Timing During Power-on Detector Operation

#### 6.6 Alarm Interrupt Function

Data set in INT1 register\_1 and register\_2 is considered as alarm time data. There is the same configuration as the hour and minute registers of the real-time data register. These registers represent hours and minutes with BCD codes. Set data must fit the date rule which is in accordance with the 12-hour or 24-hour expression that is set in status register\_1.

V0.12P

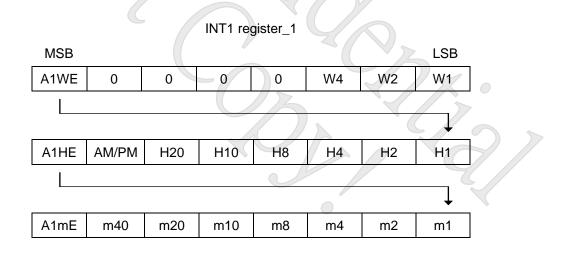

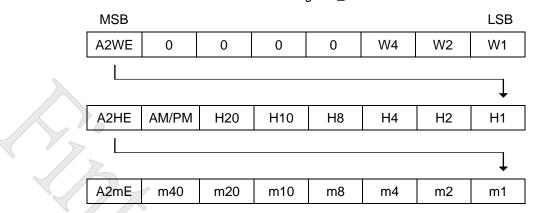

#### INT1 register\_2

In INT1 register\_1 or register\_2, A1WE/A2WE, A1HE/A2HE, and A1mE/A1mE are respectively in MSB of the day of week data, hour data, and minute data by setting "1"

#### 6.7 Clock Adjustment Function

A clock adjustment function is provided to logically perform slow/fast adjustment of the 32KHz clock and correct a slow/fast clock with high accuracy. Use the clock adjustment register to set this function. Write "00h" to disable the function. The clock adjustment register value is calculated by the following expression.

#### 6.7.1 Current Frequency > Target Frequency

$$128 - Integral\_value \begin{bmatrix} Current\_oscillatoin\_frequency\\ acutal\_measurement\_value^{*2}\\ Current\_oscillation\_frequency\\ actual\_measurement\_value^{*2} \end{bmatrix} - T \arg et\_oscillation\_frquency^{*3}\\ Minimum\_resolution^{*4}\\ Minimum\_re$$

Caution: The figure range which can be corrected is that the calculated value is from 0 to 64.

#### Note:

- \*1. The register value is the value set to the clock adjustment register. Set the binary value of this value to the clock adjustment register.

- \*2. This is the measurement value of the signal that is output to the INT1# or INT2# pin when the 1 Hz clock output setting is:

32kE = 0, INT1ME = 0, INT1FE = 1, INT1# register\_1 is 01h (for the INT1# pin) INT2ME = 0, INT2FE = 1, INT1# register\_2 is 01h (for the INT2 pin)

- \*3. This is the frequency to be adjusted by using the clock adjustment function.

- \*4. For the minimum resolution, 3.052ppm or 1.017ppm can be set using bit7 of the clock adjustment register. When bit7 is 0, 3.052ppm is set and logical slow/fast adjustment is performed every 20 seconds. When bit7 is 1, 1.017pm is set and logical slow/fast adjustment is performed every 60

seconds.

|                      | 0                   | 1                 |

|----------------------|---------------------|-------------------|

| Slow/fast Adjustment | Every 20 seconds    | Every 60 seconds  |

| Minimum Resolution   | 3.052ppm            | 1.017ppm          |

| Correction Range     | -195.3 to +195.3ppm | -65.1 to +64.1ppm |

#### 6.7.2 Current Oscillator Frequency < Target Frequency

Re gister \_value =

*Current* \_oscillator \_ frequency (*T* arg *et* \_ *oscillatoin* \_ *frequency*) actual \_ measurement \_ value Integral value (*Current* \_oscillation \_ frequency) × (*Minimum\_resolution*)

Caution: The figure range which can be corrected is that the calculated value is from 0 to 62.

#### 6.8 I2C Interface Function

The F15353 receives various commands via an I2C interface to read/write data.

#### 6.8.1 Start Condition

The start condition is established at the point where the SDA line changes from "H" to "L" when the SCL line is "H" level. All operations start with the start condition.

#### 6.8.2 Stop Condition

The stop condition is established at the point where the SDA line changes from "L" to "H" when the SCL line is "H" level. If the stop condition is received during a readout sequence, the read operation is discontinued and the device enters the standby mode.

#### 6.8.3 Data Transfer

Data transfer is performed by changing the SDA line during the period that the SCL line is "L". If the SDA line changes during the period and the SCL line is "H", it is recognized as the start or stop condition.

#### 6.8.4 Acknowledge

Data is transferred 8 bits in a row. Subsequently, in the 9th clock cycle period, the device on the system bus that is receiving the data changes the SDA line to "L" and returns the acknowledge signal to acknowledge data

reception.

#### 6.8.5 Data Reading

After detecting the start condition from outside, a device code and command are received. If the read/write bit is "1" at this point, the data read mode is entered. The data output sequence is output from the LSB.

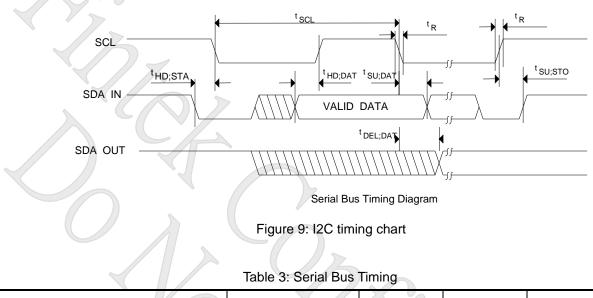

| PARAMETER                    | SYMBOL                | MIN | MAX | UNIT |

|------------------------------|-----------------------|-----|-----|------|

| SCL clock period             | t scl                 | 3   |     | uS   |

| Start condition hold time    | thd;sda               | 50  |     | nS   |

| Stop condition setup-up time | tsu;sto               | 50  |     | nS   |

| DATA to SCL setup time       | t <sub>SU;DAT</sub>   | 50  |     | nS   |

| DATA to SCL hold time        | thd;dat               | 5   |     | nS   |

| DATA OUT to SCL delay time   | t <sub>del:data</sub> | 200 |     | ns   |

| SCL and SDA rise time        | t <sub>R</sub>        |     | 200 | nS   |

| SCL and SDA fall time        | t <sub>F</sub>        |     | 200 | nS   |

|                              |                       |     |     |      |

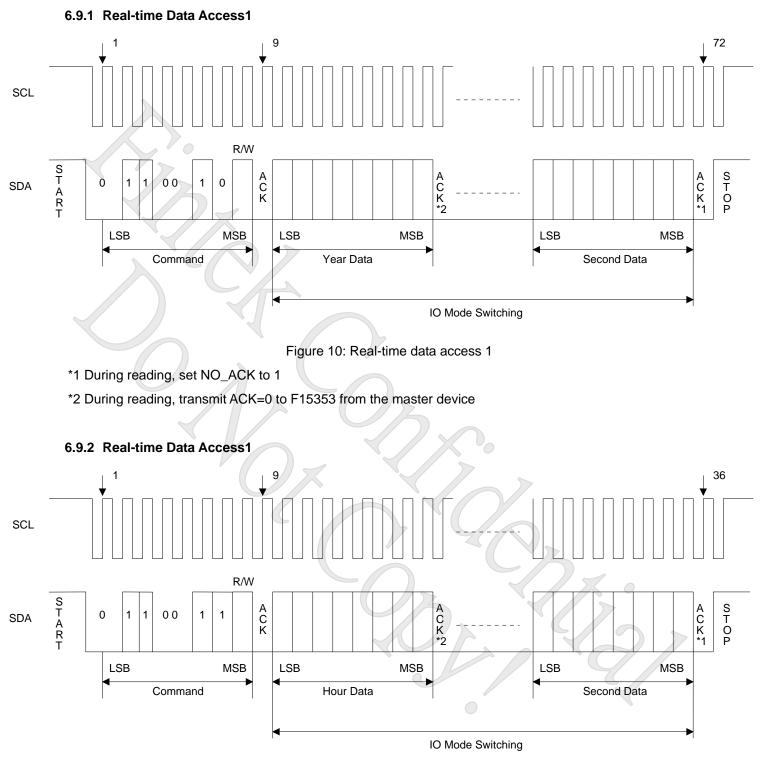

#### 6.9 Data Writing

After detecting the start condition from outside, a device code and command are received. If the read/write bit is "0" at this point, the real-time data write mode or another register write mode is entered.

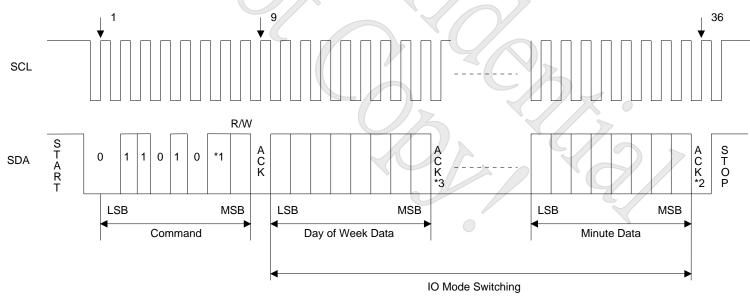

Figure 11: Real-time data access 2

\*1 Set NO\_ACK to 1 during reading

\*2 Transmit ACK=0 to F15353 from the master device during reading

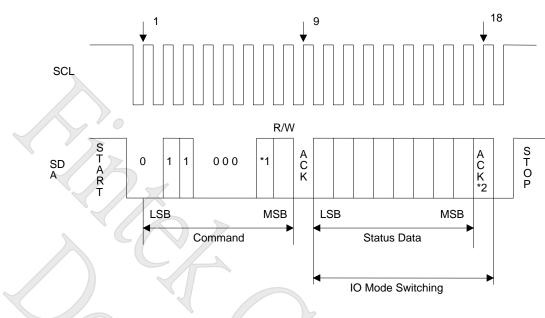

Figure 12: Status register\_1 access and status register\_2 access

\*1 0: Status Register\_1 selected, 1: Status Register\_2 selected

6.9.3 Status Register\_1 Access and Status Register\_2 Access

\*2 Set NO\_ACK to 1 during reading

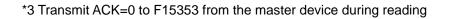

#### 6.9.4 INT1# Register\_1 Access and INT1# Register\_2 Access

Figure 13: INT1 register\_1 access and INT1 register\_2 access

\*1 0: Status Register\_1 selected, 1: Status Register\_2 selected

\*2 Set NO\_ACK to 1 during reading

Figure 14: INT1 register\_1 access and INT1 register\_2 (frequency duty data) access

- \*1 0: Status Register\_1 selected, 1: Status Register\_2 selected

- \*2 Set NO\_ACK to 1 during reading

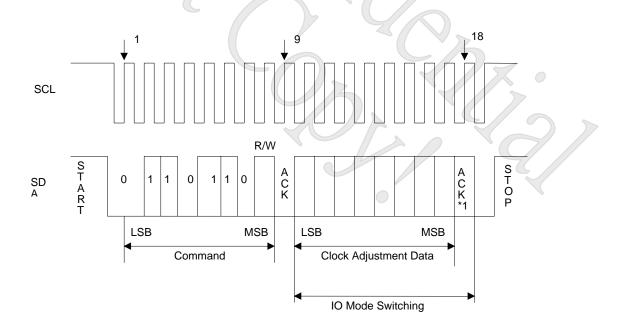

- 6.9.5 Clock Adjustment Register Access

Figure 15: Clock adjustment register access

\*1 Set NO\_ACK to 1 during reading,

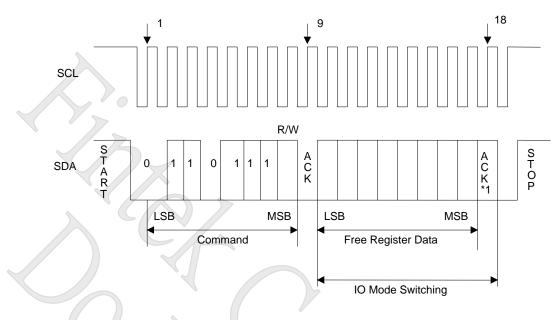

#### 6.9.6 Free Register Access

Figure 16: Free register access

\*1 Set NO\_ACK to 1 during reading,

#### 6.10 Communication Data Configuration

The master device on the system generates a start condition to the slave device to communicate. Then it transmits a 4-bit device address, 3-bit command, and 1-bit read/write command on the SDA bus. The higher 4 bits that indicate the device address are called the device code and are fixed to "0110".

|   | Device | e Code |   | Cor | mmand Code | Read/Write bit | Acknowledge bit |

|---|--------|--------|---|-----|------------|----------------|-----------------|

| 0 | 1      | 1      | 0 | C2  | C1 C0      | R/W            | ACK             |

# 7 Register Description (I2C Address = 0x6x)

| Bit | Name                     | R/W | Default    | Description                                                                         |

|-----|--------------------------|-----|------------|-------------------------------------------------------------------------------------|

|     | $\langle \gamma \rangle$ |     |            | This flag is set to "1" at power-on. Once this flag is set to "1", it is not set to |

|     |                          | 2   |            | "0" even when the power supply voltage reaches or exceeds the detection             |

| 7   | POC                      | R   | -          | voltage (VDET). This flag is read by the status register_1 access                   |

|     |                          |     |            | command. It is read-only and read-clear. When the flag is "1", it must be           |

|     |                          |     | $\bigcirc$ | initialized.                                                                        |

|     |                          |     |            | If the power supply voltage detector detects a voltage of detection voltage         |

|     |                          |     |            | (VDET) or less this flag is set to "1", which enables the detection of a            |

|     |                          |     | Ř          | power supply voltage drop. Once this flag is set to "1", it is not set to "0"       |

| 6   | BLD                      | R   | -          | even when the power supply voltage reaches or exceeds the detection                 |

|     |                          |     |            | voltage (VDET). This flag is read by the status register_1 access                   |

|     |                          |     |            | command. It is read-only and read-clear. When the flag is "1", it must be           |

|     |                          |     |            | initialized.                                                                        |

|     |                          |     | V          | When the interrupt signal is output from the INT1# pin. The INT2# flag is           |

| 5   | INT2#                    | R   | - (        | set to "1", and uses the alarm interrupt function for an interrupt signal           |

|     |                          |     |            | output from the INT2# pin.                                                          |

|     |                          |     |            | When the interrupt signal is output from the INT1# pin. The INT1# flag is           |

| 4   | INT1#                    | R   | -          | set to "1", and uses the alarm interrupt function for an interrupt signal           |

|     |                          |     |            | output from the INT1# pin.                                                          |

|     |                          |     |            | These flags configure a 2-bit SRAM type register that can be freely set by          |

| 3   | SC1                      | R/W | -          | users. They are read and written within the operating voltage range (1.3 to         |

|     |                          |     |            | 3.0 V).                                                                             |

|     |                          |     |            | These flags configure a 2-bit SRAM type register that can be freely set by          |

| 2   | SC0                      | R/W | -          | users. They are read and written within the operating voltage range (1.3 to         |

|     |                          |     |            | 3.0 V).                                                                             |

|     |                          |     |            | This flag is used to set 12-hour or 24-hour expression.                             |

| 1   | 12/24                    | R/W | -          | 0: 12-hour expression                                                               |

|     |                          |     |            | 1: 24-hour expression                                                               |

|     |                          |     |            | By setting this bit to "1", the internal IC is initialized. This is a               |

| 0   | RESET                    | W   | -          | write-only bit and is always "0" when it is read. Be sure to write "1" to the       |

|     |                          |     |            | reset flag when applying the power supply voltage to the IC.                        |

#### 7.1 Status Register\_1 Access (Command 000b)

#### 7.2 Status Register\_2 Access (Command 001b)

| Bit | Name         | R/W      | Default | Description  |                                                                         |                |                |                                      |              |   |

|-----|--------------|----------|---------|--------------|-------------------------------------------------------------------------|----------------|----------------|--------------------------------------|--------------|---|

|     |              |          |         | The TES      | T flag is a b                                                           | it for testing | g the F15353   | 3. If the TEST flag is set to "1",   |              |   |

| 7   | TEST         | R/W      | -       | the F153     | 53 is switch                                                            | ned to the T   | FEST mode.     | If this flag is "1", it is necessary |              |   |

|     |              |          |         | to initializ | e it to "0"                                                             | by setting     | the reset flag | g of status register_1 to "1".       |              |   |

|     |              |          |         | These fla    | igs are use                                                             | ed to select   | the output i   | mode from the INT2# pin. Mode        |              |   |

| 6   | INT2#AE      | R/W      | -       | selection    | s are show                                                              | n below. In    | n order to us  | e the alarm 2 function. After        |              |   |

|     |              | 2        |         | setting th   | e alarm in                                                              | terrupt mod    | de, accessin   | g INT2# register_1.                  |              |   |

|     |              | $\Box$   |         | INT2#AE      | INT2#N                                                                  | 1 INT2#F       | E II           | NT2# Pin Output Mode                 |              |   |

| 5   | INT2#ME      | R/W      |         | 0            | 0                                                                       | 0              | No inter       | rrupt                                |              |   |

|     |              |          | $\sim$  | 1            | 0                                                                       | 1              | Selecte        | d frequency steady interrupt         |              |   |

|     |              | (        |         | 1            | 1                                                                       | 0              | Pre-min        | ute steady interrupt                 |              |   |

|     |              | <b>-</b> |         | 1            | 1                                                                       | 1              | Pre-min        | ute steady interrupt 1 (50%)         |              |   |

| 4   | INT2#FE      | R/W      | - <     | 1            | 0                                                                       | 0              | Alarm ir       | nterrupt                             |              |   |

|     |              |          |         |              |                                                                         |                |                |                                      |              |   |

|     |              |          |         |              | <u> </u>                                                                |                | •              | mode from the INT1# pin. Mode        |              |   |

| 3   | 32KE         | R/W      | -       |              | selections are shown below. In order to use the alarm 1 function. After |                |                |                                      |              |   |

|     |              |          |         |              |                                                                         |                |                | g INT1# register_1.                  |              |   |

|     |              |          |         | 32KE         | INT1#AE                                                                 | INT1#M         | INT1#FE        | INT1# Pin Output Mode                |              |   |

|     |              |          |         | 0            | 0                                                                       | 0              | 0              | No interrupt                         |              |   |

| 2   | INT1#AE      | R/W      | R/W     | -            | 1                                                                       | 1              | 1              | 1                                    | 32KHz output |   |

|     |              |          |         |              |                                                                         |                |                | 0                                    | 1            | 0 |

|     |              |          |         | 0            | 1                                                                       | 1              | 0              | Pre-minute edge interrupt            |              |   |

| 1   | 1 INT1#ME    | R/W      | -       | 0            | 0                                                                       | 3              | 1              | Pre-minute edge1 interrupt (50%)     |              |   |

|     | ) INT1#FE R/ |          |         | 0            | 1                                                                       | 0              | 0              | Alarm interrupt                      |              |   |

| 0   |              | R/W      | -       | 0            | 1                                                                       | 1              | 1              | Pre-minute edge2 interrupt (50%)     |              |   |

|     |              |          |         |              |                                                                         | 1              |                |                                      |              |   |

#### 7.3 Real-time Data 1 Access, Year Data (Command 010b)

|     | Name | R/W | Default | Description                                                                 |

|-----|------|-----|---------|-----------------------------------------------------------------------------|

| 7   | Y80  | R   | -       | Refer to bit 6.                                                             |

|     | Y40  |     |         | Year data (00 to 99). Set the lower 2 digitals of the Western Calendar Year |

|     | 140  |     |         | (00 to 99) and links together with the auto calendar feature until 2099.    |

|     |      | 0   |         | For a 12-hour expression, write 0 and 1 for AM and PM, respectively. For a  |

| 6   | AMPM | R/W | -       | 24-hour expression, either 0 or 1 can be written. 0 is read when the hour   |

|     |      |     |         | data is from 00 to 11, and 1 is read when from 12 to 23.                    |

|     | m40  |     | X       | Minute data (00 to 59)                                                      |

|     | s40  |     |         | Second data (0 to 59).                                                      |

|     | Y20  |     |         | Refer to bit 6.                                                             |

|     | D20  |     |         | Day data (1 to 31)                                                          |

| 5 💊 | H20  | R/W | -       | Hour data (00 to 23 or 00 to 11)                                            |

|     | m20  |     |         | Refer to bit 6.                                                             |

|     | s20  |     |         | Relef to bit 6.                                                             |

|     | Y10  |     |         | Refer to bit 6.                                                             |

| -   |      |     |         | Month data (01 to 12). The count value is automatically changed by the      |

|     |      |     |         | auto calendar feature.                                                      |

|     | MAG  |     |         | 1 to 31: 31-day months (1, 3, 5, 7, 8, 10, 12)                              |

|     | M10  |     | -       | 1 to 30: 30-day months (4, 6, 9. 11)                                        |

| 4   |      | R/W |         | 1 to 29: 29-day months (2, leap year)                                       |

|     |      |     |         | 1 to 28: 28-day months (2, common year)                                     |

|     | D10  |     |         |                                                                             |

|     | H10  |     |         | Refer to bit 5.                                                             |

|     | m10  |     |         | Kelei to bit 5.                                                             |

|     | s10  |     |         |                                                                             |

|     | Y8   |     |         |                                                                             |

|     | M8   |     |         |                                                                             |

| 2   | D8   |     |         | Refer to bit 4.                                                             |

| 3   | H8   | R/W | -       |                                                                             |

| Ī   | m8   |     |         |                                                                             |

|     | s8   |     |         |                                                                             |

| 2   | Y4   | R/W | -       |                                                                             |

| ŀ   | M4   |     |         | Refer to bit 4.                                                             |

| ŀ   | D4   |     |         |                                                                             |

۰.

# F15353

|        | W4             |       |         | Day of week data (00 to 06)                                                |  |  |  |  |

|--------|----------------|-------|---------|----------------------------------------------------------------------------|--|--|--|--|

|        | VV4            |       |         | A septenary counter. Set it so that it corresponds to the day of the week. |  |  |  |  |

|        | H4             |       |         |                                                                            |  |  |  |  |

|        | m4             |       |         | Refer to bit 4.                                                            |  |  |  |  |

|        | s4             |       |         |                                                                            |  |  |  |  |

|        | Y2             |       |         |                                                                            |  |  |  |  |

|        | M2             |       |         |                                                                            |  |  |  |  |

|        | D2             | 3     |         |                                                                            |  |  |  |  |

| 1      | W2             | R     | Χ-      | Refer to bit 2                                                             |  |  |  |  |

|        | H2             |       |         |                                                                            |  |  |  |  |

|        | m2             |       |         |                                                                            |  |  |  |  |

|        | s2             |       |         |                                                                            |  |  |  |  |

| 4      | Y1             |       |         |                                                                            |  |  |  |  |

|        | M1             |       |         |                                                                            |  |  |  |  |

|        | D1             |       |         |                                                                            |  |  |  |  |

| 0      | W1             | R     | -       | Refer to bit 2                                                             |  |  |  |  |

|        | H1             |       |         |                                                                            |  |  |  |  |

|        | m1             | Ť     |         |                                                                            |  |  |  |  |

|        | s1             |       |         |                                                                            |  |  |  |  |

|        |                |       |         |                                                                            |  |  |  |  |

|        |                |       |         |                                                                            |  |  |  |  |

| 7.4 Re | al-time Data 2 | Acces | s, Hour | Data (Command 011b)                                                        |  |  |  |  |

| Bit    | Name           | R/W   | Default | Description                                                                |  |  |  |  |

#### 7.4 Real-time Data 2 Access, Hour Data (Command 011b)

| Bit | Name | R/W | Default | Description                                                                                                                                                                                                   |

|-----|------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | -    | -   | -       | Reserved                                                                                                                                                                                                      |

| 6   | AMPM |     |         | For a 12-hour expression, write 0 and 1 for AM and PM, respectively. For a 24-hour expression, either 0 or 1 can be written. 0 is read when the hour data is from 00 to 11, and 1 is read when from 12 to 23. |

|     | m40  |     |         | Minute data (00 to 59)                                                                                                                                                                                        |

|     | s40  |     |         | Second data (0 to 59).                                                                                                                                                                                        |

|     | H20  |     |         | Hour data (00 to 23 or 00 to 11)                                                                                                                                                                              |

| 5   | m20  | R/W | -       | Refer to bit 6.                                                                                                                                                                                               |

|     | s20  |     |         |                                                                                                                                                                                                               |

|     | H10  |     |         |                                                                                                                                                                                                               |

| 4   | m10  | R/W | -       | Refer to bit 5.                                                                                                                                                                                               |

|     | s10  |     |         |                                                                                                                                                                                                               |

•

|   | H8 |     |                       |                 |

|---|----|-----|-----------------------|-----------------|

| 3 | m8 | R/W | -                     | Refer to bit 5. |

|   |    |     |                       |                 |

|   | s8 |     |                       |                 |

|   | H4 |     |                       |                 |

| 2 | m4 | R/W | -                     | Refer to bit 5. |

|   | s4 |     |                       |                 |

|   | H2 |     |                       |                 |

| 1 | m2 | R/W | -                     | Refer to bit 5  |

|   | s2 |     | $\boldsymbol{\times}$ |                 |

|   | H1 |     |                       |                 |

| 0 | m1 | R/W |                       | Refer to bit 5  |

|   | s1 |     |                       |                 |

|   |    |     |                       |                 |

#### 7.5 INT1 Register\_1 Access (Command 100b)

#### Alarm Time1, INT1AE=0, INT1FE=0, INT2FE=0

| Bit | Name             | R/W    | Default               | Description                                                                                                                                                                                                   |

|-----|------------------|--------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | A1WE             |        |                       | A1WE, A1HE, and A1mE are respectively in the MSB of each byte. By                                                                                                                                             |

| 7   | A1HE             | R/W    | -                     | setting every bit to "1", the setting of the day of week data, hour data, and                                                                                                                                 |

|     | A1mE             |        |                       | minute data in the corresponding bye becomes valid.                                                                                                                                                           |

| 6   | AM/PM            | R/W    | R/W -                 | For a 12-hour expression, write 0 and 1 for AM and PM, respectively. For a 24-hour expression, either 0 or 1 can be written. 0 is read when the hour data is from 00 to 11, and 1 is read when from 12 to 23. |

|     | m40              |        |                       | Minute data (00 to 59)                                                                                                                                                                                        |

| 5   | H20              | R/W    | -                     | Hour data (00 to 23 or 00 to 11)                                                                                                                                                                              |

| 5   | m20              | - R/W  |                       | Minute data (00 to 59)                                                                                                                                                                                        |

| 4   | H10              |        | R/W - Refer to bit 5. | Pofer to hit 5                                                                                                                                                                                                |

| +   | m10              | 17/10  |                       |                                                                                                                                                                                                               |

| 3   | H8               | R/W    |                       | Refer to bit 5.                                                                                                                                                                                               |

| 5   | m8               | 17/10  | -                     |                                                                                                                                                                                                               |

|     | W4               |        |                       | Day of week data (00 to 06)                                                                                                                                                                                   |

| 2   | VV- <del>1</del> | R/W    | / -                   | A septenary counter. Set it so that it corresponds to the day of the week.                                                                                                                                    |

| 2   | H4               | 1.7.44 |                       | Refer to bit 5.                                                                                                                                                                                               |

|     | m4               |        |                       |                                                                                                                                                                                                               |

| 1   | W2               | R/W    | -                     | Refer to bit 2                                                                                                                                                                                                |

۰.

### F15353

|   | H2 |     |   |                 |

|---|----|-----|---|-----------------|

|   | m2 |     |   |                 |

|   | W1 |     |   |                 |

| 0 | H1 | R/W | - | Refer to bit 1. |

|   | m1 |     |   |                 |

#### Frequency Mode (INT1ME=0, INT1FE=1)

| Bit                                                                                    | Name | R/W | Default | Description                                                                 |  |

|----------------------------------------------------------------------------------------|------|-----|---------|-----------------------------------------------------------------------------|--|

|                                                                                        |      | R/W | XC.X    | Data set in INT1 register_1 is considered as frequency duty data. By settin |  |

|                                                                                        |      |     |         | each bit from bit[4:0] of the register to "1", the frequency corresponding  |  |

| 7.5                                                                                    | SC   |     |         | each bit is selected in an ANDed form. The SC bits configure a 3-bit SRAI   |  |

| 7:5                                                                                    | SC   |     |         | type register that can be set freely by users. These bits can be read an    |  |

|                                                                                        |      |     |         | written within the operating voltage range (1.3 to 3.0 V). There is no impa |  |

|                                                                                        |      |     |         | on the duty function                                                        |  |

| 4                                                                                      | 16Hz | R/W | -       | Write 1 to set frequency to 16Hz                                            |  |

| 3                                                                                      | 8Hz  | R/W | 1       | Write 1 to set frequency to 8Hz                                             |  |

| 2                                                                                      | 4Hz  | R/W | -       | Write 1 to set frequency to 4Hz                                             |  |

| 1                                                                                      | 2Hz  | R/W | -       | Write 1 to set frequency to 2Hz                                             |  |

| 0                                                                                      | 1Hz  | R/W | 1-1     | Write 1 to set frequency to 1Hz                                             |  |

| 7.6 INT1 Register_2 Access (Command 101b)<br>Alarm Time2, INT2AE=0, INT2FE=0, INT2FE=0 |      |     |         |                                                                             |  |

| D.1                                                                                    | NL   |     |         |                                                                             |  |

#### 7.6 INT1 Register\_2 Access (Command 101b)

#### Alarm Time2, INT2AE=0, INT2FE=0, INT2FE=0

| Bit | Name      | R/W     | Default | Description                                                                   |

|-----|-----------|---------|---------|-------------------------------------------------------------------------------|

|     | A2WE      |         |         | A2WE, A2HE, and A2mE are respectively in the MSB of each byte. By             |

| 7   | A2HE      | E R/W   |         | setting every bit to "1", the setting of the day of week data, hour data, and |

|     | A2mE      | 1       |         | minute data in the corresponding bye becomes valid.                           |

|     | AM/PM     | R/W     | -       | For a 12-hour expression, write 0 and 1 for AM and PM, respectively. For a    |

| 6   |           |         |         | 24-hour expression, either 0 or 1 can be written. 0 is read when the hour     |

| 0   |           |         |         | data is from 00 to 11, and 1 is read when from 12 to 23.                      |

|     | m40       |         |         | Minute data (00 to 59)                                                        |

| 5   | H20       | R/W     |         | Hour data (00 to 23 or 00 to 11)                                              |

| 5   | m20 R/W - |         | -       | Minute data (00 to 59)                                                        |

| 4   | H10       | - R/W - |         | Refer to bit 5.                                                               |

| 4   | m10       |         | -       |                                                                               |

۰.

|   |      |         |                         | F15353                                                                     |

|---|------|---------|-------------------------|----------------------------------------------------------------------------|

| 3 | H8   | R/W     | -                       | Refer to bit 5.                                                            |

| 0 | m8   | 10,00   |                         |                                                                            |

|   | 10/4 |         |                         | Day of week data (00 to 06)                                                |

| 2 | W4   | R/W     |                         | A septenary counter. Set it so that it corresponds to the day of the week. |

| Ζ | H4   | r./ v v | -                       | Refer to bit 5.                                                            |

|   | m4   |         |                         |                                                                            |

|   | W2   |         |                         |                                                                            |

| 1 | H2   | R/W     | -                       | Refer to bit 2                                                             |

|   | m2   |         | $\overline{\mathbf{X}}$ |                                                                            |

|   | W1   |         |                         |                                                                            |

| 0 | H1   | R/W     |                         | Refer to bit 1.                                                            |

|   | m1   |         |                         |                                                                            |

|   |      |         |                         |                                                                            |

#### Frequency Mode (INT2ME=0, INT2FE=1)

| Bit | Name                                              | R/W | Default | Description                                                                  |

|-----|---------------------------------------------------|-----|---------|------------------------------------------------------------------------------|

|     |                                                   | R/W |         | Data set in INT1 register_2 is considered as frequency duty data. By setting |

|     |                                                   |     |         | each bit from bit[4:0] of the register to "1", the frequency                 |

| 7.5 | 66                                                |     |         | corresponding to each bit is selected in an ANDed form. The SC bit           |

| 7:5 | 7:5 SC                                            |     |         | configure a 3-bit SRAM type register that can be set freely by users. These  |

|     |                                                   |     |         | bits can be read and written within the operating voltage range (1.3 to 3.0  |

|     |                                                   |     |         | V). There is no impact on the duty function                                  |

| 4   | 16Hz                                              | R/W | -       | Write 1 to set frequency to 16Hz                                             |

| 3   | 8Hz                                               | R/W | -       | Write 1 to set frequency to 8Hz                                              |

| 2   | 4Hz                                               | R/W | -       | Write 1 to set frequency to 4Hz                                              |

| 1   | 2Hz                                               | R/W | -       | Write 1 to set frequency to 2Hz                                              |

| 0   | 1Hz                                               | R/W | -       | Write 1 to set frequency to 1Hz                                              |

| 770 | 7 Clock Adjustment Pegister Access (Command 110b) |     |         |                                                                              |

#### 7.7 Clock Adjustment Register Access (Command 110b)

| Bit | Name | R/W | Default | Description                                                                  |

|-----|------|-----|---------|------------------------------------------------------------------------------|

| 7   | V7   | R/W | -       | The clock adjustment register is a 1-byte register that is used to logically |

| 6   | V6   | R/W | -       | correct real-time data. When not using the clock adjustment register, set    |

| 5   | V5   | R/W | -       | this register to 00h using the clock adjustment register write command.      |

| 4   | V4   | R/W | -       |                                                                              |

| 3   | V3   | R/W | -       |                                                                              |

| 2   | V2   | R/W | -       |                                                                              |

| 1 | V1 | R/W | - |

|---|----|-----|---|

| 0 | V0 | R/W | - |

## 7.8 Free Register Access (Command 111b)

| Bit | Name | R/W | Default                 | Description                                                               |

|-----|------|-----|-------------------------|---------------------------------------------------------------------------|

| 7   | F7   | R/W | -                       |                                                                           |

| 6   | F6   | R/W | -                       |                                                                           |

| 5   | F5   | R/W | -                       | The free register is a 1-byte SRAM type register that can be set freely t |

| 4   | F4   | R/W | ×-                      | users. It can be read and written within the operating voltage range (1.3 |

| 3   | F3   | R/W | $\overline{\mathbf{x}}$ | 3.0 V).                                                                   |

| 2   | F2   | R/W | -                       |                                                                           |

| 1   | F1   | R/W | -                       |                                                                           |

| 0   | F0   | R/W |                         |                                                                           |

۰.

# 8 Ordering Information

| Part Number | Package Type            | Production Flow          |

|-------------|-------------------------|--------------------------|

| F15353S     | 8-SOP (Green Package)   | Commercial, 0°C to +70°C |

| F15353G     | 8-TSSOP (Green Package) | Commercial, 0°C to +70°C |

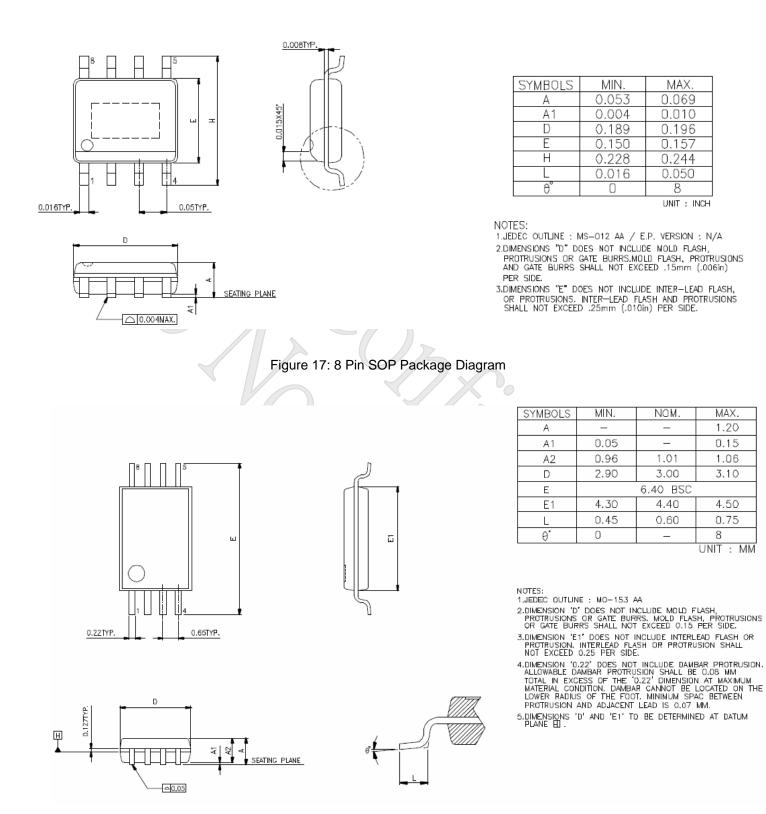

# 9 Package Dimensions (8-SOP, 8-TSSOP)

Figure 18: 8 Pin TSSOP Package Diagram

Feature Integration Technology Inc.

Headquarters

3F-7, No 36, Tai Yuan St., Chupei City, Hsinchu, Taiwan 302, R.O.C. TEL : 886-3-5600168 FAX : 886-3-5600166 www: http://www.fintek.com.tw

#### Taipei Office

Bldg. K4, 7F, No.700, Chung Cheng Rd., Chungho City, Taipei, Taiwan 235, R.O.C. TEL : 866-2-8227-8027 FAX : 866-2-8227-8037

Please note that all datasheet and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this datasheet belong to their respective owner

۰.

# **10 Application Circuit**